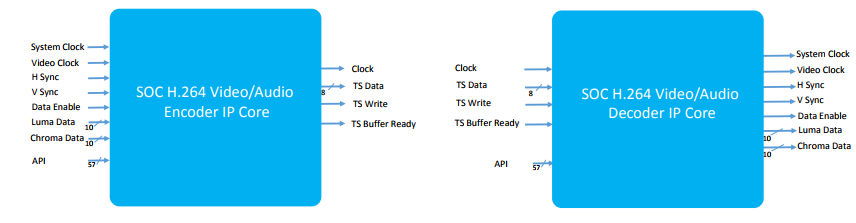

SOC offers high-performance H.264 IP Cores, H.265 IP Cores, and MPEG-2 IP Cores for encoding and decoding video in real-time. SOC's MPEG Codec IP Cores are built using highly parallel all-hardware architecture without the use of processors, known for their for low latency, low power-consumption, and small silicon footprint.

The IP Core format offers the greatest degree of design flexibility, suitable for integration onto mid-range Xilinx and Intel FPGAs.

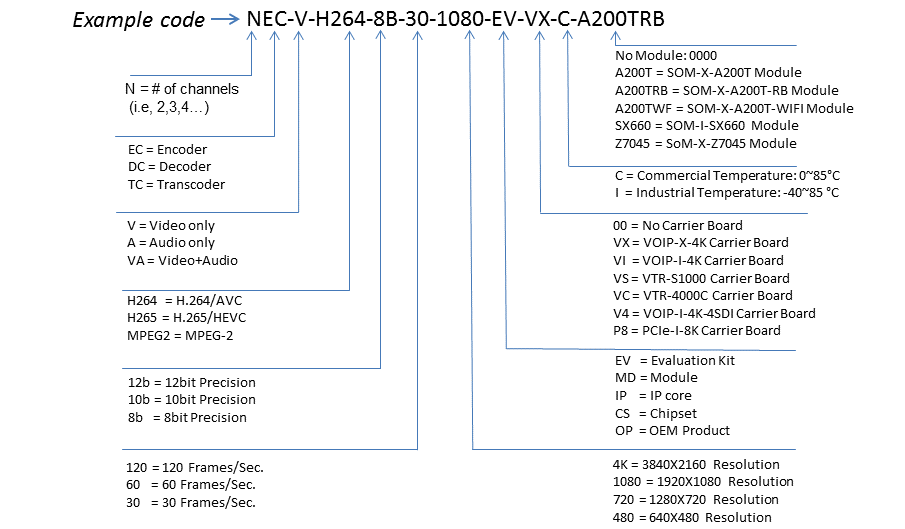

|  |  |  |  |  |  |  |

SOC IP Cores are designed to work on mid-level Intel and Xilinx FPGAS and SoCs.

Designed with a focus on video quality, SOC's MPEG Codec IP Cores are tested vigurously using a wide range of quality, latency, and performance benchmarks.

SOC's all-hardware architecture executes many stages in parallel every clock cycle, which enables zero-latency capture-to-display solutions. SOC's 0.25ms latency is among the lowest on the market, and is superior compared to processor-based and DSP-based alternatives.

Power savings can mean longer battery life for wireless applications like solar-powered/remote surveillance, portable HD cinematography, and FPV drone/vehicle control; or huge power cost savings for cloud video-processing operations.

IP Cores are designed targeting mid-range off-the-shelf XILINX and Intel FPGAs and SoCs. Slim IP core versions are available which further reduce logic resource utilization for resource-constrained systems.

Over 200 API regsiters are accessible which control run-time parameters in the Encoding pipleine. Allowing you to alter the bitrate, group-of-pictures, and fine tune highly specific aspects of the engine.