# SOC Generic Decoder System

# **API Specification**

Revision: 1.3 2017.4.26

© 2017 SOC Technologies Inc.

SOC is disclosing this user manual (the "Documentation") to you solely for use in the development of designs to operate with SOC hardware devices. You may not reproduce, distribute, republish, download, display, post, or transmit the Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of SOC. SOC expressly disclaims any liability arising out of your use of the Documentation. SOC reserves the right, at its sole discretion, to change the Documentation without notice at any time. SOC assumes no obligation

to correct any errors contained in the Documentation, or to advise you of any corrections or updates. SOC expressly disclaims any liability in connection with technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU "AS-IS" WITH NO WARRANTY OF ANY KIND. SOC MAKES NO OTHER WARRANTIES, WHETHER EXPRESSED, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY RIGHTS. IN NO EVENT WILL SOC BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

© 2008-2017 SOC, Inc. All rights reserved.

SOC, the SOC logo, the Brand Window, and other designated brands included herein are trademarks of SOC, Inc.

### **Revision History**

The following table shows the revision history for this document.

| Date       | Comment                              | Revision | Author |

|------------|--------------------------------------|----------|--------|

|            | Old versions                         | 1.0      |        |

| 2016.10.24 | Added register BF to the API manual. | 1.1      | Blake  |

| 2016.12.20 | Audio PID selectable (0x92)          | 1.2      | Chad   |

| 2017.04.26 | Add DDR calib register(0x40)         | 1.3      | Blake  |

#### Introduction

The API interface has 256 register (16 bit for writing and 32 bits for reading). Each register has an address to allow user-access. The registers accept command code for controlling the operation of the features within the FPGA. The registers may be read to acquire status and debugging information.

Some registers are allocated for user configurations and the rest are reserved for system functions such as debugging. The following table(s) specifies the address, definition, and access right (read/write) for the user-accessible registers. Note: registers of any API\_TYPE that are NOT in the table are not designed for user access. If such a register is written to, the decoder may stop running. To recover, the core must be re-downloaded into the FPGA.

### Control the API inside the FPGA

If it is necessary to control the API via the modules inside the FPGA, the ports of the API are available. Details, including the clock frequency, are provided in the corresponding integration manual.

## Control the API outside the FPGA

If it is necessary to control the Decoder from outside the FPGA, the address, date, and R/W pins can be routed to the FPGA I/O pins. The desired FPGA I/O pins for the API may be selected or the SOC default pins may be used. An UART interface is available, upon request. The interface provides access to the API via uart\_tx and uart\_rx pins.

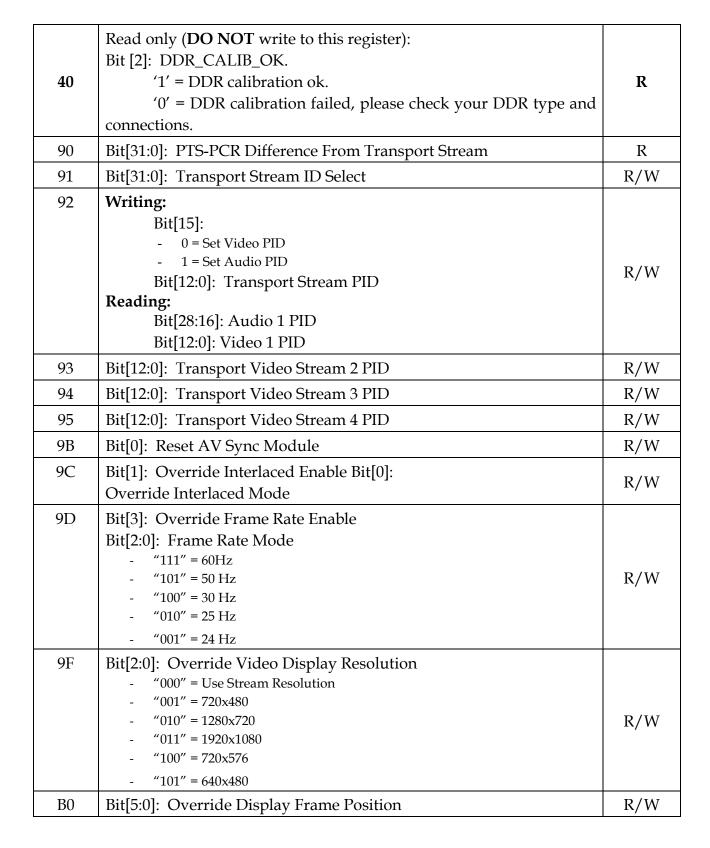

#### **Table-1: General Core Registers**

| Addr  | Information | Access |

|-------|-------------|--------|

| (HEX) | momation    | Access |

|    | - Only used when 0xB1=2                                                                                                                                                                                                                                                                                                                                                                                             |     |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| B1 | Bit[1:0]: Override Display Frame Mode<br>- "00" = Normal A/V Sync<br>- "01" = Display Last Decoded<br>- "10" = Display Frame reference by register 0xB0 - "11" = Display<br>current Decoding Frame                                                                                                                                                                                                                  |     |

| B3 | <ul> <li>Bit[12]: Enable Auto Low Delay mode. (May not be compatible with all TS stream). This function will auto adjust the video presentation time to the lowest possible.</li> <li>Bit[11]: Truncate active video range for compliance with TRS embedded video codes.</li> <li>Bit[10]: Allow expired frame to be display if newer than current displayed frame</li> <li>Bit[8]: Debug Overlay Enable</li> </ul> | R/W |

| B4 | Bit[4]: TS MPEG2 Stream Detected Bit[3]:<br>TS H264 Stream Detected                                                                                                                                                                                                                                                                                                                                                 | R   |

| В5 | Bit[15:12]: TS Rx Sync Error Counter (user clock)<br>Bit[11:8]: TS Rx Sync Error Counter (TS clock)<br>Bit[7:4]: TS Rx Byte Count (TS clock)<br>Bit[3:0]: TS Rx Byte Count (user clock)                                                                                                                                                                                                                             | R   |

| B6 | Bit[31:16]: TS Buffer Overflow Count Bit[15:0]:<br>TS Demux Overflow Count                                                                                                                                                                                                                                                                                                                                          | R   |

| B7 | Bit[1]: Bypass PCR Sync (PCR counter will free run) Bit[0]:<br>New Stream Sync                                                                                                                                                                                                                                                                                                                                      | R/W |

| B8 | <ul> <li>Bit[15:0]: PCR resync threshold.</li> <li>PCR will only resync if difference is greater than the threshold.<br/>This allows the system to tolerate variable jitter</li> </ul>                                                                                                                                                                                                                              | R/W |

| BF | Display timing threshold value (DTH):<br>Bit [2:0]: DTH for progressive stream. The <b>unit</b> is a frame. Bit<br>[10:8]: DTH for interlaced stream. The <b>unit</b> is the first field,<br>typically the top field.                                                                                                                                                              |      |  |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|

|    | <ul> <li>*This register is to control latency for progressive and interlaced scenario, respectively.</li> <li>DTH =0: The frame is submitted to display only when the whole (100%) unit is received and decoded. This is the default and most safe value.</li> <li>DTH =1 to 7: The frame is submitted to display when DTH x12.5 % of the unit is received and decoded.</li> </ul> | R/W  |  |

|    | <b>***Important notes:</b> Be careful to use this register with a low value. Due to the input stream is possibly not constant coming, the low value (for                                                                                                                                                                                                                           |      |  |

|    | <i>example</i> DTH =2 <i>for only</i> 25% <i>) could cause the display jitter or flashing. If this happen, the user should increase the</i> DTH.                                                                                                                                                                                                                                   |      |  |

| FC | Bit[31:0]: Decoder System Build Date                                                                                                                                                                                                                                                                                                                                               | R    |  |

| FD | Bit[31:0]: Decoder System Time Stamp                                                                                                                                                                                                                                                                                                                                               | R    |  |

| FE | Bit[11]: MPEG2 Core PresentBit[10]: H264 Core PresentBit[3]: PCM Buffer PresentBit[7]: DSP Interface Core PresentBit[5]: Video Output Core PresentBit[4]: Maximum 1080i OutputBit[3]: 50Hz minimum output frame rateBit[2]: Watermark PresentBit[1]: FPGA DNA Authentication presentBit[0]: FPGA EEPROM Authentication present                                                     | R    |  |

| FF | Bit[31:16]: Reset Count<br>Bit[6]: Transport Stream Mode<br>Bit[5]: Transport Stream Reset<br>Bit[4]: Video Decoder Reset<br>Bit[3]: Authentication Key OK<br>Bit[2]: PTS Reset Enable*<br>Bit[1]: Display Reset*<br>Bit[0]: Decoder Reset*                                                                                                                                        | R/W* |  |

## **Table-2: Frame Sync API registers description**

| Addr<br>(HEX) | Information                                                                             | Access |

|---------------|-----------------------------------------------------------------------------------------|--------|

| 70            | Bit[31:16]: Output Expired Frame Counter Bit[15:0]:<br>Output Frame Counter             | R      |

| 71            | Bit[15:0]: Input Invalid Frame Counter                                                  | R      |

| 72            | Bit[15:0]: Input Expired Frame Counter                                                  | R      |

| 73            | Bit[15:0]: PCR Clock Resync Counter                                                     | R      |

| 74            | Bit[15:0]: Frames Duplicated                                                            | R      |

| 75            | Bit[15:0]: Frames Skipped                                                               | R      |

| 76            | Bit[1]: Trick Mode Running Bit[0]:<br>Override Sync*                                    | R/W*   |

| 77            | Bit[5:0]: Buffer Frame Count                                                            | R      |

| 78            | Bit[31:24]: Top Field Count<br>Bit[23:16]: Bottom Field Count<br>Bit[15:0]: Frame Count | R      |

| 7D            | Bit[31:0]: Current Presentation Time                                                    | R      |

| 7E            | Bit[31:0]: Last Displayed Presentation Time                                             | W      |

#### **Table-3: DDR Fifo Registers**

The DDR fifo is a miniumum 8MB buffer to handle any incoming bandwidth spikes the BRAM is not sufficient for. In most application the DDR fifo will remain empty or below 10%.

| Addr<br>(HEX) | Information           | Access |

|---------------|-----------------------|--------|

| 30            | Bit[31:0]: Build Date | R      |

| 31 | Bit[14]: Reset                                       |        |

|----|------------------------------------------------------|--------|

|    | Bit[13]: Buffer Overflow                             |        |

|    | Bit[10]: Byte Read                                   |        |

|    | Bit[9]: Output Buffer Empty                          |        |

|    | Bit[8]: Output Buffer Ready                          | R/W    |

|    | Bit[3]: Timer Enabled*                               |        |

|    | Bit[2]: Low Delay*                                   |        |

|    | Bit[1]: Clear Buffer Overflow Register*              |        |

|    | Bit[0]: API Reset*                                   |        |

| 32 | Bit[5:0]: Burst Size                                 | D /147 |

|    | Bit[8]: Bypass DDR Fifo (DDR will not be used)       | R/W    |

| 33 | Bit[25:0]: DDR Start Address                         | R      |

| 34 | Bit[25:0]: DDR End Address                           | R      |

| 35 | Bit[7:0]: DDR Buffer Percent                         | R      |

| 36 | Bit[7:0]: DDR Buffer Count (Number of Blocks in DDR) | R      |

| 37 | Bit[15:0]: Input Count                               | R      |

| 38 | Bit[15:0]: Read Count                                | R      |